A Comprehensive to N-Channel JFET

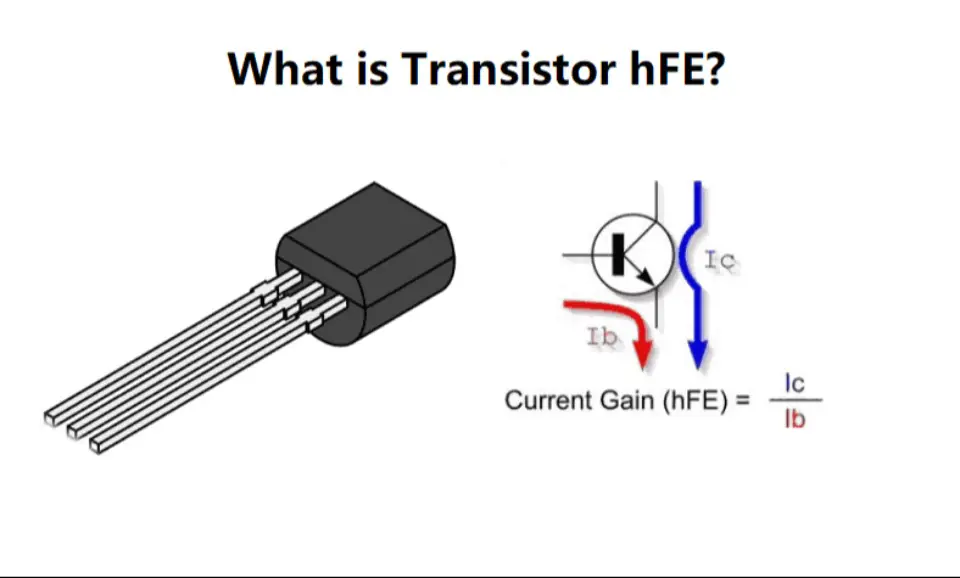

The junction field-effect transistor, or JFET, is a semiconductor device with three terminals. In this unipolar device, the voltage applied to one terminal regulates the current flowing between the other two, constituting the output circuit current.

Functioning as a unijunction, depletion mode device, the Junction Field Effect Transistor (JFET) can use a gate voltage with minimal leakage to modulate channel current with high linearity. Renowned for low noise and high radiation tolerance, JFETs are excellent transistors for various applications demanding precise high-gain amplification.

JFETs come in two types: n-channel and p-channel. Because electrons exhibit faster mobility than holes, n-channel JFETs are more prevalent than p-channel JFETs. In this article, we’ll delve into N-channel JFET, explore its diagram, symbol, operation and the difference between P-channel JFET etc. Everything you need to know about this transistor.

What is N-Channel JFET?

An N-channel JFET incorporates an N-type material between the drain and source terminals. Two P-type materials are integrated along the metal contacts of the gate terminal. Including these two P-type materials results in the formation of two PN junctions within the JFET transistor.

Why the name JFET?

The device's fundamental functionality relies on the biasing of the pn junction. In this case, the junction is reverse-biased, controlling the channel's width and regulating the current flowing between the Drain and Source. The pn junction is pivotal in the device's operation, hence the nomenclature Junction Field-Effect Transistor (JFET).

Biasing of an N-channel JFET

The cross-sectional illustration above depicts an N-type semiconductor channel with a P-type region known as the Gate diffused into the N-type channel, creating a reverse-biased PN-junction. This junction, responsible for forming the depletion region around the Gate area when no external voltages are applied, categorizes JFETs as depletion mode devices.

The depletion region generates a potential gradient with varying thickness around the PN-junction, restricting the current flow through the channel by reducing its effective width and consequently increasing the overall resistance of the channel.

Notably, the most-depleted segment of the depletion region lies between the Gate and the Drain, while the least-depleted area is between the Gate and the Source. Consequently, the JFET's channel conducts with zero bias voltage (i.e., the depletion region has near-zero width).

In the absence of an external Gate voltage (VG = 0) and a small voltage (VDS) applied between the Drain and the Source, the maximum saturation current (IDSS) flows through the channel from the Drain to the Source, limited only by the small depletion region around the junctions.

Upon applying a small negative voltage (-VGS) to the Gate, the depletion region's size begins to increase, reducing the overall effective area of the channel and thus decreasing the current flowing through it—a kind of "squeezing" effect occurs. Therefore, the depletion region's width increases by applying a reverse bias voltage, reducing the channel's conduction.

The PN-junction is reverse biased, so minimal current flows into the gate connection. Further, making the Gate voltage (-VGS) more negative decreases the width of the channel until no more current flows between the Drain and the Source, and the FET is considered "pinched-off" (similar to the cut-off region for a BJT). The voltage at which the channel closes is termed the "pinch-off voltage" (VP).

N-Channel JFET Diagram

Figure 1 illustrates the schematic of the n-channel JFET. The configuration presented in this diagram simplifies the examination of JFET principles.

Figure 1

On both sides of the device, heavily doped p-type regions with acceptor impurities form gate G. Observe the interconnection between the two p-type regions and the gate terminal.

The space between the two gate regions constitutes the channel, comprised of n-type material. This narrow semiconductor channel establishes a conductive pathway between the source and the drain. Most carriers enter the device through source S and exit through drain D. The source side can be positioned at either end of the channel.

The fundamental operation of this structure involves modifying the resistance between the S and D terminals by adjusting the voltage on gate G.

N-Channel JFET Symbol

Figure 2 illustrates the circuit symbol, current direction conventions, and voltage polarity conventions for an n-channel JFET.

Figure 2

The arrowhead at the gate signifies the direction across the junction from the p-type to the n-type JFET.

Is represents conventional current entering at S.

Id represents conventional current entering at D.

Ig represents conventional current entering at G. This is the direction of gate current flow when the gate junction is forward-biased.

Vds denotes the applied drain-to-source voltage – positive if D is more positive than S.

Vdd stands for the drain supply voltage (external voltage source).

Vgg stands for the gate supply voltage (external voltage source).

Vgs signifies the applied gate-to-source voltage – positive if G is more positive than S. Vgs is utilized with a polarity to reverse-bias the p-n junction (Vgs = - Vgg).

For an n-channel JFET, Id and Vds are positive, while Is and Vgs are negative.

N-channel JFET Operation

Before applying an external voltage to the JFET terminals, it's important to note that, under no-bias conditions, two p-n junctions form a carrier-depletion or space-charge region at each junction. In this state, excess carriers (electrons) have been depleted from these regions, rendering them incapable of supporting conduction (see Figure 1).

In Figure 3, Vgs is set to 0 V with the gate and source short-circuited, while Vds has a low positive value. The positive drain terminal attracts electrons in the channel, resulting in a current Id.

Figure 3 Vgs = 0 V and Vds > 0 V

Following the conventional current direction, Id enters D. Simultaneously, Is, with the same magnitude as Id, is defined as entering S; therefore, Is is negative under this condition. Ig, the gate current, is negligibly small, a notable characteristic of JFET.

The channel's impedance limits the charge flow magnitude in Figure 3. It's worth noting that the carrier-depletion regions widen towards the D side. Assuming a uniformly distributed resistance, the voltage drop in the channel increases from 0 V at S to Vds at D. Consequently, the p-n junctions become increasingly reverse-biased from S to D.

As the reverse bias across the junctions grows, so does the thickness of the region of immobile uncovered charges. These uncovered charges, comprising negative ions on the p-type side and positive ions on the n-type side, create a dipole charge layer at the junction. The electric field lines originating on the positive ions and terminating on the negative ions contribute to the voltage drops across the junctions. This mechanism, where current control results from the extension of the field associated with the region of uncovered charges with increasing reverse bias, is aptly described as the field effect.

Figure 4 illustrates the source-drain characteristic of an n-channel JFET, depicting Id vs. Vds with Vgs = 0.

Figure 4 Id vs. Vds, Vgs = 0 V.

When Id is 0, the channel is open. As Vds increases to a few volts, the current follows ohm’s law linearly, resulting in an almost straight-line plot. This behaviour is due to the constant resistance, with the n-type JFET acting as a simple semiconductor resistor.

Incrementing Vds widens the depletion regions, causing the conducting part of the channel to shrink progressively. This reduces the effective width of the channel, increasing its resistance. The shrinking is more pronounced at distances farther from the source due to the ohmic drop along the channel.

Figure 5. Vgs = 0 V, Vds = Vp.

Continuing to increase Vds, as depicted in Figure 5, eventually leads to a condition known as pinch-off, where Vds = Vp (pinch-off voltage). At pinch-off, the curve in Figure 4 levels off, and Id approaches a constant value – the saturation level denoted as Idss (saturated short-circuit drain current). The channel’s resistance tends toward infinite ohms in the horizontal region of the curve. At pinch-off, a tiny channel with high-density current remains.

In Figure 5, the channel is on the brink of pinch-off at the drain end. Further increasing Vds beyond Vp extends the contact of the two depletion regions along the channel, but Idss remains constant. In this state, the JFET operates as a current source.

The channel cannot fully close at pinch-off, reducing Id to zero. Instead, Id maintains the saturation level shown in Figure 4. If Id were to drop to zero, the ohmic drop causing the reverse bias along the p-n junction would disappear, eliminating the depletion region responsible for pinch-off.

Vgs Providing Additional Reverse Bias

The JFET is regulated by the gate-to-source voltage (Vgs). Gradually reducing the gate terminal's potential relative to the source generates a set of Id vs. Vds curves, with Vgs as a variable. Figure 6 illustrates typical curves for an n-channel JFET.

Figure 6

Applying a gate voltage (Vgs) in the direction that increases reverse bias establishes depletion regions similar to Vgs = 0, but at lower Vds levels. This leads to pinch-off and saturation occurring at smaller Vds values. Lowering Vds aids in producing pinch-off, causing it to happen at a reduced drain current.

Applying a slight positive voltage to the gate in the direction of forward bias increases the Vds required for pinch-off. However, applying high positive voltages is inconvenient to avoid undesirable currents at the gate terminal.

Like previous cases, each characteristic curve has an ohmic region for small Vds values (Id proportional to Vds) and a constant current region for large Vds values, where Id marginally responds to Vds. Beyond the pinch-off level, the pinch-off channel limits the current to the magnitude at pinch-off.

Figure 6 also reveals a parabolic drop in the pinch-off voltage and the saturation current magnitude decreases as Vgs becomes more negative. When Vgs = -Vp, producing a saturation level with minimal Id current, the transistor is considered "off."

As Vds reach higher magnitudes, the curves rise to seemingly infinite levels, indicating avalanche breakdown across the p-n junctions. Under this condition, only the output circuit elements limit the current through the channel.

The maximum voltage that can be applied between any two JFET terminals is the lowest, causing avalanche breakdown across the p-n junction. Figure 6 shows that an avalanche occurs at lower Vds values as the gate experiences more reverse bias. This happens because the reverse-bias gate voltage (Vgs) adds to the drain voltage (Vds), escalating the voltage across the p-n junction.

Characteristics of N-channel JFET

The figure below illustrates the transconductance curve of the N-channel JFET, graphed between drain current and gate-source voltage. The transconductance curve exhibits distinct regions: ohmic, saturation, cutoff, and breakdown.

Ohmic Region:

This is the only region where the transconductance curve demonstrates a linear response. Here, the drain current opposes the JFET transistor resistance, defining the Ohmic region.

Saturation Region:

In the saturation region, the N-channel junction field-effect transistor is active in the ON condition. The maximum current flows due to the applied gate-source voltage.

Cutoff Region:

The cutoff region signifies the absence of drain current flow. Consequently, the N-channel JFET is in the OFF condition during this phase.

Breakdown Region:

If the applied VDD voltage at the drain terminal exceeds the required maximum voltage, the transistor fails to resist the current. Consequently, the current flows from the drain terminal to the source terminal, causing the transistor to enter the breakdown region.

How to Turn on an N-Channel JFET

To turn on an N-channel JFET, provide a positive voltage +VDD to the drain terminal of the transistor while keeping the gate terminal voltage at 0V. This setup enables the flow of current through the drain-source channel. Without a voltage (0V) applied to the gate, VG, the drain current reaches its maximum safe value, placing the N-channel JFET in the ON active region.

Therefore, when a sufficiently positive voltage, VDD, is applied and no voltage (0V) at the base, the N-channel JFET operates at its maximum capacity with the highest current.

How to Turn Off an N-Channel JFET

To turn off the N-channel JFET, you have two options. You can disconnect the positive bias voltage, VDD, which supplies power to the drain or introduce a negative voltage to the gate. The drain current decreases when a negative voltage is applied to the gate. As the gate voltage, VG becomes more negative, the current diminishes until cutoff, indicating that the JFET has entered the OFF region.

N-Channel JFET Applications

Due to their distinctive characteristics, Junction Field-Effect Transistors (JFETs) find widespread application across various domains. Here are a few noteworthy examples:

- Amplifiers: The commendable combination of high input impedance and low noise attributes renders JFETs suitable for deployment in diverse amplifier types, such as audio amplifiers, RF amplifiers, and instrumentation amplifiers.

- Switches: JFETs serve as efficient electronic switches. Their voltage-controlled nature allows them to handle high-frequency signals with minimal noise interference.

- Buffer Circuits: Leveraging their elevated input impedance, JFETs are frequently employed in buffer circuits. In this capacity, they adeptly isolate different stages within an electronic system.

- Oscillators: The excellent frequency response of JFETs makes them conducive to oscillator construction, contributing to their role in generating oscillating signals.

N-Channel JFET Advantages & Disadvantages

Advantages

Here are several benefits associated with Junction Field-Effect Transistors (JFETs):

- High Impedance: JFETs exhibit elevated impedance levels, contributing to their effectiveness in electronic applications.

- Low Power Consumption: JFETs are characterized by low power consumption, making them energy-efficient devices.

- Compact Size: The fabrication of JFETs in smaller sizes allows them to occupy minimal space within circuits, enhancing their spatial efficiency.

Disadvantages

Below are a few disadvantages associated with Junction Field-Effect Transistors (JFETs):

- Low Gain-Bandwidth Product: JFETs exhibit a low gain-bandwidth product, impacting their overall performance in certain applications.

- Frequency-Dependent Performance: The performance of JFETs tends to be affected as the frequency increases, primarily due to internal capacitance-induced feedback.

Commonly Available N-Channel JFETs

| 2N5457 | A versatile N-Channel JFET known for its high input impedance and precise voltage control, making it suitable for various electronic applications. |

| J201 | Another popular N-Channel JFET with low noise and high gain characteristics, often used in audio amplifiers and signal processing circuits. |

| BF256B | This N-Channel JFET is well-regarded for its low noise and high gain properties, making it suitable for applications where signal fidelity is crucial. |

| J113 | Known for its low leakage current and high gain, the J113 is commonly used in low-frequency amplifier circuits and switching applications. |

| MPF102 | A widely used N-Channel JFET with medium gain. |

What is the Difference Between N-Channel JFET and P-Channel JFET

The only difference is that in an n-channel JFET, current is conveyed by electrons, whereas in a p-channel JFET, it is transported by holes. In JFET, the p-n junction between the gate and source is consistently maintained in reverse-biased conditions.

Final Words

In conclusion, this comprehensive guide has unravelled the mysteries of N-Channel JFET. From their construction to operation and applications, you are now equipped with the knowledge to make informed decisions in electronic circuit design.

Read More

FAQ

-

What is JFET?

JFET, or Junction Field Effect Transistor, is one of the most straightforward field-effect transistors. Unlike the Bipolar Junction Transistor, JFETs operate as voltage-controlled devices.

-

What is a JFET used for?

JFETs represent three-terminal semiconductor devices applicable for electronic switch or resistor functions and amplifier construction.

-

What is the function of an N-Channel JFET?

N-channel JFETs primarily function as voltage-controlled resistors, allowing precise control over current flow in electronic circuits.

-

What is the difference between JFET and MOSFET?

Due to its variable transconductance, the MOSFET exhibits greater noise levels than the JFET. In contrast, JFETs have limitations in handling high power dissipation compared to MOSFETs. With their ability to manage higher power dissipation, MOSFETs are well-suited for high-power switching applications. Additionally, MOSFETs tend to be smaller in size compared to JFETs.

-

Why use JFET instead of MOSFET?

JFETs are more cost-effective to manufacture, exhibit greater gain, and feature a flatter characteristic curve than MOSFETs. These qualities render JFETs well-suited for applications requiring low noise and high impedance.

Dr. James Anderson

Dr. James Anderson

Still, need help? Contact Us: [email protected]